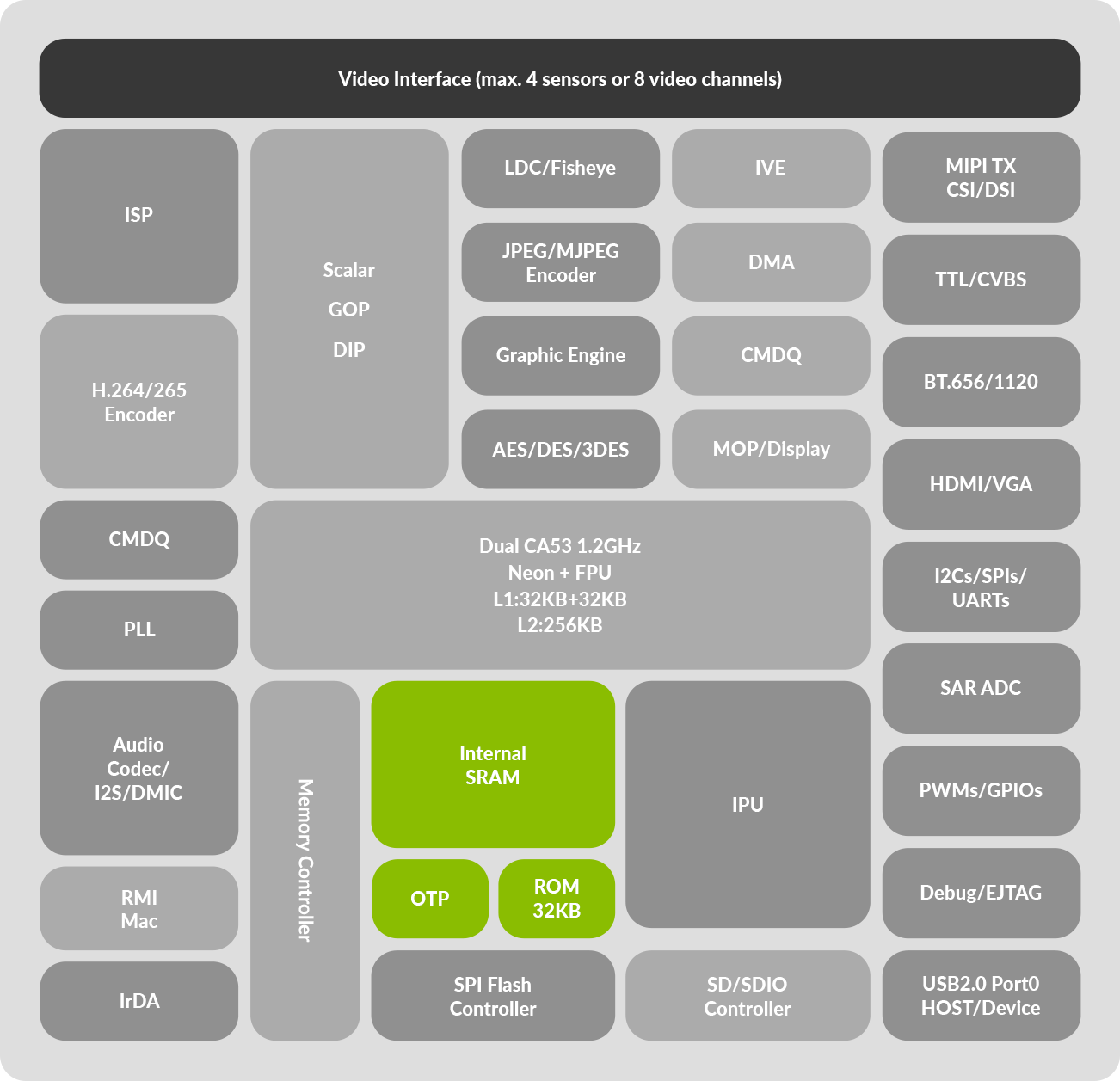

High Performance Processor Core

ARM Cortex-A53 Dual Core with max. clock rate 1.2GHz

32KB L1 I-cache and 32KB L1 D-cache

256KB L2 cache

Neon and FPU

Stand-alone voltage domain

Video Input Interface

Two sets of BT.601-like 12-bit parallel interface for Bayer

or YUV422 data input, with data rate up to 150MP/s

Two sets of BT.656 8/10-bit parallel interface for YUV422

data input, with data rate up to 300MB/s (DDR mode)

Each BT.656 input can support both SDR and DDR mode

with 1-to-1, 1-to-2, and 1-to-4 TDM mode

One set of BT.1120 16-bit parallel interface for YUV422

data input, with data rate up to 600MB/s (DDR mode)

BT.1120 input can support SDR and DDR mode with 1-to-1

and 1-to-2 mode

Two sets of MIPI RX interface, each block supporting 4-lane data x1

or 2-lane data x2

MIPI CSI-2 ver. 1.1 and D-PHY ver. 1.1

MIPI RX virtual channel 1 to 4

MIPI RX data rate up to 1.5Gbps

MIPI RX supports special data input like TOF, PDAF, and Gyro data

Supports max. 4-CH HDR video input or 8-CH YUV video input

Image Signal Processor

Supports up to 8M (4096×2160) pixels video recording and

image snapshot

Bad pixel compensation

Noise Reduction (NR)

Optical black correction

Lens shading compensation

Auto White Balance (AWB) / Auto Exposure (AE) / Auto Focus (AF)

CFA color interpolation

Color correction

Gamma correction

Wide Dynamic Range (WDR)

Rotation with 90 or 270 degrees

Mirror and flip

High Dynamic Range (HDR) with two exposure frames

Lens distortion correction and Fisheye mode

Fully programmable multi-function scaling engines

Graphics overlap process with RGB or Index mode and private

region block mode

Multiple read/write DMAs for flexible image processing

Dual channels for Bayer and YUV data process

H.265/HEVC Encoder

Fully compatible with ISO/IEC 23008-2 High Efficiency video coding

Main Profile, Level 5.0 encode

Supports I-frame and P-frame

1/4-pixel precision motion vectors

Deblocking filter and Sample Adaptive Offset(SAO)

Picture/CTU/subCTU level rate control

Region of Interest (ROI) encoding with custom QP map

H.264/AVC Encoder

Compatible with the ITU-T Recommendation H.264 specification

Baseline/Constrained Baseline/Main/High Profile, Level 5.1 encode

1/4-pixel precision motion vectors

In-loop deblocking filter

CABAC/CAVLC support

Error resilience tools

Frame level and MB level rate control

Region of Interest (ROI) encoding with custom QP map

H.265/HEVC Decoder

Fully compatible with ISO/IEC 23008-2 High Efficiency

Video Coding Main Profile

HEVC Main Profile, Level 5.0 decode

Supports resolution from 8×8 to 4096×4096

I/P/B slices

Prediction Unit (PU): 64×64 to 4×4

Transform Unit (TU): 32×32 to 4×4

1/4 motion compensation with 8-tap filters

High performance CABAC decoding

In-loop deblocking filtering

Sample adaptive offset (SAO)

Error concealment

8 bit DVP

20/16/14/12/10/8 bit 1/2/4 lane MIPI

16/12/10/8 bit 1/2/4 lane LVDS

H.264/AVC Decoder

Compatible with the ITU-T Recommendation H.264 specification

Baseline/Constrained Baseline/Main/High Profile, Level 5.1 decode

Supports resolution from 8×8 to 4096×4096

Variable block size (16×16, 16×8, 8×16, 8×8, 8×4, 4×8 and 4×4)

CABAC/CAVLC support

In-loop deblocking filter

Error detection, concealment and error resilience tools

JPEG/MJPEG Encoder/Decoder

PEG/MJPEG baseline encoding or decoding

YUV422 or YUV420 format

Max. 4096×4096 frame resolution

Supports real-time mode and frame encode mode

Video Codec Performance

4K@45fps H.265/H.264 encoding or decoding

4K (3840×2160)@30fps JPEG/MJPEG encoding

4K (3840×2160)@15fps JPEG/MJPEG decoding

Intelligence Processing Unit (IPU)

Max. clock rate 1.0GHz

Programmable 8/16-bit process

Supports RGB/YUV data format R/W DMA

Stand-alone voltage domain

AI computing performance reaches 0.8TOPs

Intelligent Video Engine (IVE)

Supports 30 functions (CSC/Filter/Erode/Dilate/SAD/3×3/DOT, etc.)

for video analysis

Max. resolution 1920×1080

Read/Write DMA

Audio Processor

Two stereo ADCs with max. 4-CH single-ended or differential

microphone inputs

One stereo DAC with max. 2-CH single-ended

Supports 8K/16K/32KHz sampling rate audio recording

ADC and DAC SNR over 92dB

Digital and analog gain adjustment

One I2S interface with input max. 8-ch and output 2-ch TDM mode

I2S master or slave mode with 16- or 32-bit data and 8/16/32/48/96/192K

sampling rate

Supports 4-CH DMIC (1 clock + 2 data)

Video Output Interface

Dual read DMAs and display channels

Supports 16 preview windows and 1 PIP window rotation and overlap

Picture quality enhancement (gamma, AWB, contrast, saturation,

sharpness, brightness, 3×3 matrix)

Each display channel can output to MIPI/TTL/HDMI/CVBS/VGA lineout

TTL/Parallel-RGB interface, 16/24-bit, 1280×720@60fps

Serial-RGB interface, 8/16-bit, 800×480@60fps

i80 TFT LCD panel, 8/16/18-bit, 320×240@30fps

MIPI DSI TX, RGB 16/18/24-bit, 2560×1600@60fps

MIPI CSI TX, RGB/YUV, 3840×2160@30fps

MIPI TX virtual channel 1 to 4

MIPI TX data rate up to 1.5Gbps

BT.656/1120 interface, 8/16-bit, up to 1920×1080@30fps

BT.601-like/BT.656 output 8-bit progressive mode or BT.1120

16-bit progressive mode YUV format

HDMI v1.4b with 3840×2160 30fps

VGA output up to 1920×1200 60fps

NTSC/PAL interlace mode

Simultaneous HDMI+VGA output

Scale-down and write-back DMA

SPI NOR/NAND Flash Interface

Compliant with standard, dual and quad SPI flash memory components

Max. 108MHz clock rate

SD/eMMC Interface

SD card 2.0 x1 and SD card 3.0 (SDR104 or SDR50/DDR50) x1,

data bus 1/4-bit mode

SDIO 2.0 (SDR25) x1 and SDIO 3.0 (SDR50)x1, data bus 1/4-bit mode

eMMC ver4.3 with 4/8 data bit and max. 50MHz clock rate

USB Interface

USB2.0 port0 configurable Host or Device

− Device mode supports 7 endpoints (3 for UVC and 3 for CDC)

USB2.0 port1 Host

− Host mode supports EHCI specifications

DRAM Memory

External 16-bit DDR3/DDR3L x2 or 32-bit LPDDR3 x1

Supports memory space up to 16Gb

Data rate up to 2133Mbps

Connectivity

Built-in 10/100M Ethernet MAC x2 with RMII interface

One USB 2.0 Host Controller

One SDIO 2.0 Host Controller

Security Engines

FIPS 140-1 compliant random number generator

Embedded OTP (One Time Programmable) memory

to store secure and calibration data

Boot Options

ROM (32KB)

SPI NOR

SPI NAND

SD Card

eMMC

USB2.0 device mode

Peripherals

Dedicated GPIOs for system control GPIOs)

Supports up to 11 PWM outputs (shared with)

Up to four generic UARTs and one fast UART with flow control

Three generic timers and one watchdog timer

Up to three SPI masters

Up to six I2C Masters

− Supports 1to4 mode x1

− Supports 1to2 mode x2

Built-in 10-bit SAR ADC with 4-channelanalog inputs

for different kinds of application

Supports IrDA

Supports RTC with 32768Hz crystal I/F

Supports POR (Power On Reset)

Supports internal temperature sensor

Supports ISP sensor clock 12MHz, 24MHz, 37.125MHz

Operating Voltage Range

VDD: 0.92V~1.0V

CPU VDD: 0.95V~1.02V

IPU VDD: 0.95V~1.02V

I/O: 1.8/3.3V

DRAM: 1.5/1.35

Power Consumption: TBD.

Package

Moisture Sensitivity Level: 3